You have not yet added any article to your bookmarks!

Join 10k+ people to get notified about new posts, news and tips.

Do not worry we don't spam!

Post by : Anis Farhan

Artificial intelligence has evolved well beyond its foundational software beginnings. Modern AI systems rely on substantial computational capacities, making hardware efficiency a crucial element in determining the size, speed, and potential of any model. Each leap in performance directly links to how effectively a chip can manage large data sets. Leading companies aren't merely improving their models; they're fabricating advanced chips aimed at minimizing energy usage, enhancing data transfer speeds, and making AI implementations scalable. In this age, silicon has become a pivotal strategy.

Transistor advancements lie at the heart of every significant hardware breakthrough. The semiconductor industry has transitioned from traditional FinFET technologies to Gate-All-Around (GAA) and nanosheet designs. This evolution allows for better current flow regulation, increased transistor density, and reduced power loss—integral to satisfying AI's expanding need for computing power.

Next-generation chips featuring 3nm and 2nm nodes are now incorporating billions of transistors within compact designs, ushering in greater performance levels while maintaining lower power usage. Achieving this progress demands extensive material research, precision manufacturing, and significant capital. However, each new process node reshapes what chip designers can accomplish, paving the way for faster, more efficient AI accelerators.

GPUs have historically served as the backbone of AI training due to their capacity for parallel computing. However, as AI models become more diverse, new hardware architectures are emerging. Domain-specific accelerators—like ASICs, tensor cores, and NPUs—are specifically designed to boost machine learning tasks while consuming less power and achieving greater throughput.

These specialized chips perform matrix operations, convolutional tasks, and mixed-precision computations more effectively compared to general GPUs. Consequently, companies are now developing custom chips tailored for various applications such as natural language processing, recommendation systems, or edge AI, fostering reductions in training duration and overall operational costs.

Speed involves more than just sheer computing power; it also pertains to how swiftly data can be transmitted. Advances in memory technologies, including high-bandwidth memory (HBM) and 3D-stacked DRAM, facilitate closer proximity of data to processing units, significantly curbing latency. Additionally, chiplet-based design—where several smaller dies are combined—has transformed chip innovation.

This modular method enhances production yields, cuts costs, and permits the integration of specialized dies manufactured on diverse process nodes. For AI, this translates to merging compute, memory, and connectivity into a single high-performance unit, ensuring both scalability and energy efficiency in a compact model.

Advancements in hardware alone cannot drive progress without concurrently developed software that fully utilizes its capabilities. This co-design philosophy—optimally aligning software and hardware—is now central to innovation. Contemporary AI frameworks and compilers are engineered to reduce data movement, merge operations, and effectively manage workloads across numerous cores.

These advanced compilers convert higher-level programming into machine language fine-tuned for specific chip architectures, maximizing performance squeezing potential. As collaboration deepens between hardware engineers and software developers, AI systems become increasingly efficient.

The expansive energy consumption of AI demands a shift towards more efficient practices. Contemporary chips emphasize energy use in tandem with speed. Strategies such as dynamic voltage adjustment, adaptive frequency control, and low-precision computations lead to significant power savings without sacrificing accuracy.

Designers are turning their focus to sustainable AI—developing chips that require fewer watts to execute tasks. When coupled with smarter data center cooling methods and renewable power sources, this approach ensures AI growth aligns with environmental principles. Energy efficiency is now a global imperative.

Recent global events have highlighted the tech sector's reliance on a limited number of semiconductor production centers. To address this, governments and businesses are diversifying manufacturing and significantly investing in domestic facilities. This strategic realignment aims to secure chip supply chains, minimize geopolitical risks, and foster technological autonomy.

In this evolving landscape, various regions are competing to establish advanced fabrication plants capable of producing high-performance AI chips. This diversification fosters innovation and braces the industry against supply interruptions, contributing to a more equitable global semiconductor landscape.

The AI hardware market is diverging into two distinct spheres: expansive hyperscalers and smaller, nimble innovators. Major tech organizations are building extensive computing frameworks for cutting-edge AI models, whereas startups and researchers are pursuing cost-effective but powerful options.

Cloud services are tackling this gap by providing tiered access to AI hardware, allowing smaller entities to train and launch models without the burden of hefty capital. Moreover, open-source hardware initiatives and effective inference chips are democratizing access, ensuring the progress in AI remains inclusive and broadly accessible.

Inference, the process where AI models generate predictions, requires both speed and high efficiency. Specialized inference chips and NPUs are uniquely devised for this purpose, allowing for real-time processing in devices such as smartphones, sensors, and autonomous systems.

By facilitating intelligence at the edge, these chips lessen reliance on cloud infrastructures, enhance privacy, and enable quicker response times. They are instrumental in powering technologies ranging from virtual assistants and autonomous vehicles to intelligent cameras and health-monitoring wearables. Edge AI hardware signifies the next evolution in computing—intimate, private, and immediate.

As chips become denser and more potent, effective heat management has developed into a specialized field. Innovative cooling techniques, including liquid immersion and direct-to-chip systems, are now vital for preserving performance and reliability in AI data centers.

Operators are also incorporating renewable energy generation and heat repurposing into their facility designs, promoting sustainability in high-performance computing. Each watt conserved in cooling can translate into additional computing power, signaling that infrastructure innovation is equally crucial as chip evolution.

While existing chips push silicon to its limits, research continues to explore possibilities beyond it. Photonic computing leverages light over electricity to convey data, promising ultra-fast, low-heat information processing. Neuromorphic chips mimic human neural patterns, offering astounding efficiencies for event-based workloads.

Quantum accelerators, though in early development, may ultimately handle complex optimization and simulation tasks infeasible for classical systems. Collectively, these pioneering concepts suggest a forthcoming era where AI hardware transcends conventional capacities, merging physics and computing in groundbreaking ways.

As custom hardware becomes prevalent, new challenges arise in maintaining trust and reliability. Hardware-level safeguards now encompass defenses against side-channel vulnerabilities, embedded threats, and unauthorized access.

Verification methodologies ensure chip integrity from design through deployment, while runtime authenticity checks ensure that only trusted code executes on sensitive platforms. These security measures are increasingly indispensable as AI hardware is utilized in critical areas such as national defense, healthcare, and financial sectors where reliability and confidentiality are paramount.

The hardware ecosystem for AI thrives on collaborative efforts. Open standards relating to interconnectivity, packaging, and APIs guarantee that chips from various manufacturers integrate seamlessly. This interoperability permits organizations to combine diverse components into coherent systems, eliminating vendor restrictions.

Promoting transparency and compatibility, standardization accelerates adoption and innovation. As the AI domain matures, such open ecosystems will sustain an appropriate balance between competition and collaboration.

Organizations must adopt a hardware-focused perspective in their AI planning. This approach requires developing applications that can adapt to ongoing chip advancements while balancing scalability and reliability from the cloud and on-premises environments.

Businesses should prioritize performance-per-watt, memory capacity, and long-term availability when selecting hardware partners. Incorporating adaptability into procurement and training practices ensures resilience as the industry advances swiftly. In the evolving AI landscape, astute hardware strategies will translate into lasting competitive advantages.

The future of AI will be defined not solely by algorithms but by the chips that empower these algorithms. Each evolution in transistors, advancements in packaging, and architectural reconfigurations brings us closer to systems that are faster, more intelligent, and sustainable.

Chips form the silent yet potent driving force behind intelligent machines, acting as critical engines of advancement. Understanding their transformation enables us to anticipate AI's trajectory toward enhanced accessibility, efficiency, and alignment with our world's physical boundaries.

This article serves informational purposes only. It outlines general trends and insights into AI hardware development and should not be interpreted as investment, technical, or engineering recommendations. Readers are encouraged to consult original research and industry documentation for comprehensive technical analysis.

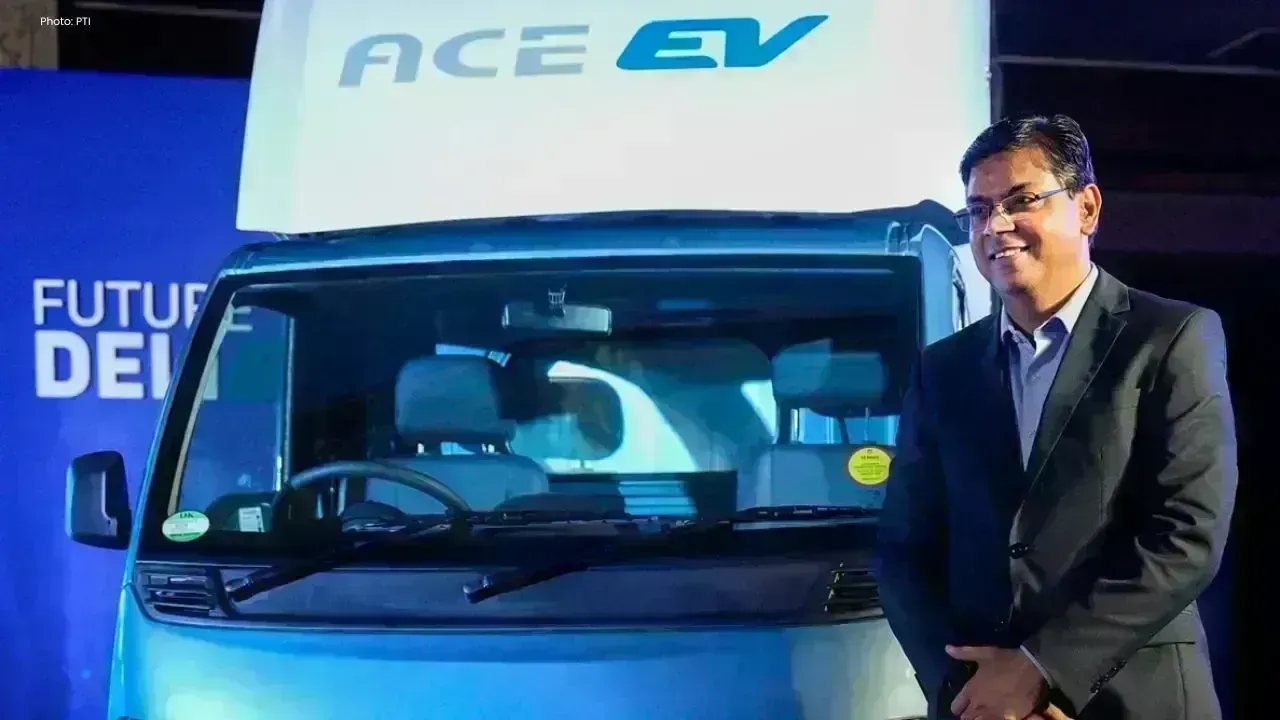

China Electric Trucks Boom Amid Energy Crisis

Electric truck sales surge in China as rising fuel prices and Iran conflict push shift towards clean

Man Dies in Road Accident in Taungoo Township

A 23-year-old man died after a truck and motorcycle collision in Taungoo, raising concerns over road

Vietnam Election Sees Record Voter Turnout

Vietnam reports 99.7% voter turnout in 2026 elections, highlighting strong public participation and

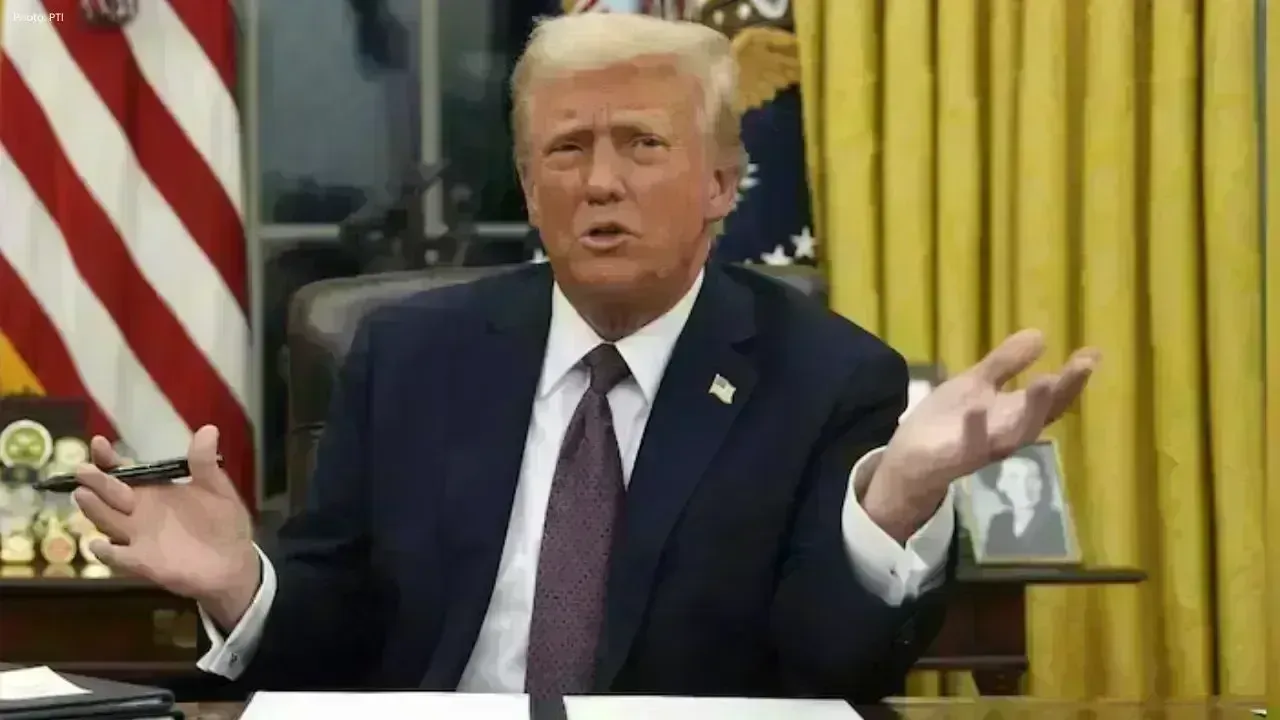

Trump Threatens Iran Amid US Pilot Rescue

Trump warns of strikes on Iran if Strait of Hormuz stays shut, as US rescues downed aviator and tens

Starbucks Seals China Deal, Plans Expansion

Starbucks partners with Boyu Capital, selling majority stake in China unit while targeting rapid sto

Three Charged in 510kg Meth Trafficking Case

Three suspects, including a married couple, face High Court trial in Malaysia over 510kg meth haul,